Ingrid Basanta(1), Santiago Lemus(2)

Universidad Nacional Experimental Politécnica

"Antonio José de Sucre"

Vicerrectorado Puerto Ordaz

Catedra de Circuitos Digitales Configurables

1. Introducción

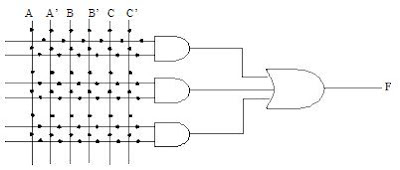

Las PAL (Arreglos Lógicos Programables), que como su nombre lo indica son arreglos matriciales de fusibles y diodos que mediante una cierta lógica pueden llegar a desempeñar cualquier función booleana. Su arquitectura interna consiste en términos AND programables que alimentan términos OR fijos. Todas las entradas a la matriz pueden ser combinadas mediante AND entre si, pero los términos AND específicos se dedican a términos OR específicos. Las PAL tienen una arquitectura muy popular y son probablemente el tipo de dispositivo programable por usuario más empleado. Si un dispositivo contiene macrocélulas, comúnmente tendrá una arquitectura PAL.

Las PAL son PLD que se han desarrollado para superar ciertas desventajas de la PLA, tales como los largos retardos debidos a los fusibles adicionales que resultan de la utilización de dos matrices programables y la mayor complejidad del circuito. Básicamente la PAL está formada por una matriz AND programable y una matriz OR fija con la lógica de salida, esta estructura permite implementar cualquier suma de productos lógica con un número de variables definido, sabiendo que cualquier función lógica puede expresarse como suma de productos. La PAL es el dispositivo lógico programable más común y se implementa con tecnología bipolar TTL o ECL.

2- Arreglos Lógicos Programables (PAL)

Un dispositivo lógico programable es aquel cuyas características pueden ser modificadas y almacenadas mediante programación. Entre los dispositivos lógicos programables el PAL es el más simple, son los más populares y los más utilizados.

El circuito interno de un PAL consiste de una matriz de conexiones, una matriz de compuertas AND programables y un arreglo de compuertas OR fijo [1]. La matriz de conexiones es una red de conductores distribuidos en filas y columnas con un fusible en cada punto de intersección, mediante la cual se seleccionan cuales entradas del dispositivo serán conectadas al arreglo OR y así obtener una función lógica en forma de suma de productos. Los circuitos PAL son no reprogramables; ya que la síntesis de las ecuaciones lógicas se realiza a través de la quema de fusibles en cada punto de intersección de los pines de entrada con las compuertas.

3. Estructura de la PAL

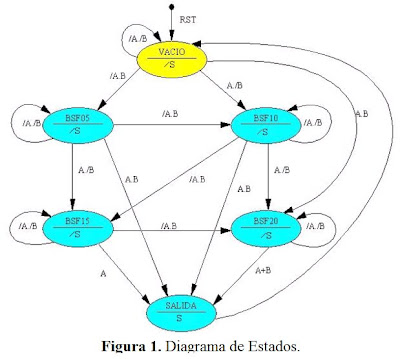

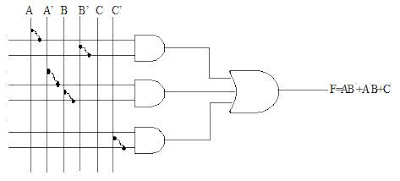

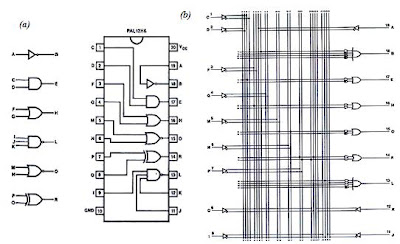

En la Figura 1 se muestra la estructura interna de una PAL, en esta se observa que cada línea de salida es conectada a tres líneas producto y por consiguiente representa una suma de tres términos producto.

Figura 1. Estructura interna de la PAL.

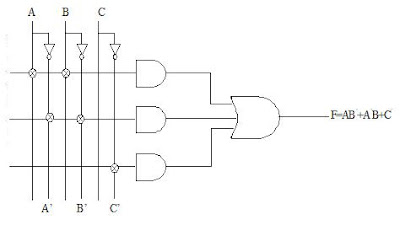

Debido al arreglo OR, la representación del PAL mostrada en la Figura 2 es más usada que el de la Figura 1.

Figura 2. Estructura interna de la PAL estándar.

4. Funcionamiento de la PAL.

Como se ha mencionado, las PAL están formadas por una matriz de puertas AND programable conectada a una puerta OR fija. Esta estructura permite implementar cualquier suma de productos lógicos con un número de variables definidas y limitadas, entre otras, por el número de entradas y salidas que tenga el dispositivo.

En la Figura 3 se muestra la estructura básica de un PAL para tres variables de entrada y salida sin programar [2]. Cada punto de intersección entre una fila y una columna se denomina celda y es el elemento programable de la PAL. Cada fila se conecta a la entrada de una puerta AND y cada columna a la variable de entrada o su complemento. En función de la presencia o ausencia de las conexiones creadas por programación, se puede aplicar cualquier combinación de variables de entrada o sus complementos a una puerta AND para generar cualquier operación producto que se desee.

Figura 3. PAL con matriz AND sin programar.

La implementación de una función lógica sobre un PAL, se muestra la figura 4, donde las señales que entran a la matriz son las variables de entrada y sus complementos. Cuando se requiere la conexión entre una fila y una columna, el fusible queda intacto, Cuando dicha conexión no se requiere, el fusible se abre en el proceso de programación. La salida de la puerta OR proporciona finalmente la suma de productos. Observe que si alguna entrada de una puerta AND queda sin conectar, esta adquiere el valor del elemento neutro del producto lógico, sin afectar el resultado de dicha puerta.

Figura 4. PAL con matriz AND programada.

5. Símbolo simplificado de la PAL.

Puesto que las PAL son circuitos integrados muy complejos desde el punto de vista interno, los fabricantes han adoptado una notación simplificada para eliminar los diagramas lógicos complicados. En la Figura 5 se muestra la notación.

Figura 5. Símbolo simplificado de una PAL.

Buffer de entrada: Para evitar cargar con la gran cantidad de entradas de puertas AND a las que se pueden conectar una variable o su complemento, se añade un buffer a las variables de entrada de la PAL. Un buffer inversor genera el complemento de una variable de entrada.

Puertas AND: una matriz AND de una puerta PAL típica tiene una gran cantidad de líneas de interconexión y cada puerta AND tiene entradas múltiples. El diagrama lógico de una PAL muestra cada puerta AND que realmente tienen varias entradas, utilizando una sola línea para representar a todas las líneas de entrada.

Conexiones de una PAL: Para obtener un diagrama lo más sencillo posible, los fusibles de una matriz AND programable se indican mediante una X en el punto de intersección si el fusible queda intacto y no se indica nada sí el fusible esta fundido. Las conexiones fijas emplean el punto estándar.

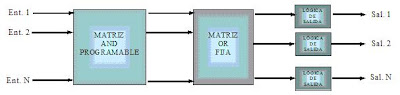

6. Diagrama de bloque de una PAL.

Las salidas de la matriz AND son las entradas de la matriz OR y la salida de cada puerta OR se asocia a una variable lógica de salida. Una PAL típica tiene ocho o más entradas en la matriz AND y hasta ocho bloques lógicos de salida como se muestra en la Figura 6 [3].

Figura 6. Diagrama de bloque de una PAL.

Algunas PAL disponen de pines de entrada/salida (E/S) combinados, que se pueden programar como salida o como entrada. La presencia de estos pines es muy útil cuando se desea, por ejemplo, realizar una realimentación entre variables de salida y entrada como es el caso del diseño de un biestable.

7. Fabricantes de la PAL.

Dispositivos PAL (o simplemente PALS) se introducen en 1978 por Monolithic Memories, Inc., (MMI), la arquitectura era más sencilla que la FPLA porque omitía la matriz OR programable. Esto hizo los dispositivos más rápidos, más pequeños y más baratos [4].

Los PAL de MMI pronto fueron distribuidos por AMD la cual empleo tecnología PROM de fusibles Titanio-Tungsteno programables una sola vez; Texas Instruments apoya las PALs con arquitectura variable programables una sola vez y National Semiconductor, quien fue el pionero en el desarrollo de Arreglos Lógicos Programables (Programmable Logic Arrays, PLA’s) en forma de un DIP grande de 24 pines o terminales (0.6 pulgadas de ancho) con 96 términos productos, 14 entradas, 8 salidas.

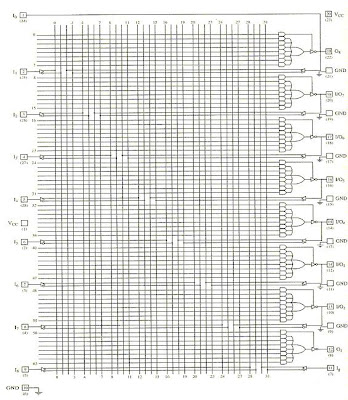

El primer circuito PAL fue el 16L8, de 20 terminales (pines), con soporte para 8 salidas y hasta 16 entradas con tecnología Bipolar, mostrada en la Figura 7, en cada macro celda se observa:

° Cada variable de entrada es distribuida negada y sin negar en la matriz de intersección mediante los literales (columnas).

° Todas las columnas cruzan líneas horizontales donde se puede realizar el AND cableado de las columnas que se elijan y con ello generar en cada fila la suma de productos que se desee.

° Siete filas son unidas mediante una compuerta OR para realizar la suma de productos.

° La señal de salida es negada por cuestiones de velocidad; ya que es más rapida una compuerta NOR que una OR, aunque existe la PAL 16H8, donde la salida en la compuerta OR sale sin negar.

° En algunas macroceldas el valor de salida se realimenta negado y sin negar a todo el circuito, lo cual permite la conexión en cascada de lógica, para la síntesis de funciones más complejas. Esto además facilita el diseño de circuitos realimentados para la elaboración de celdas de emorias.

° Las salidas se pueden controlar individualmente a través de las compuertas Tri-State de cada una y con esto poder seleccionar la salida como entrada.

Figura 7. PAL16L8 en encapsulado DIP20.

Con este tipo de dispositivos pueden simularse arreglos del tipo de Productos Lógicos, o en su caso realizar decodificación de direcciones. Sin embargo, la mayor aportación de los dispositivos PAL fue generar aplicaciones específicas en muy corto tiempo. La operación de estos dispositivos inicio manejando velocidades de 4.7 Mhz para la IBM PC hasta 33 Mhz, para posteriormente alcanzar los 50 Mhz; hoy se pueden encontrar dispositivos que operan con un retraso de propagación de la señal del orden de 5ns.

Sin embargo, su estructura simple también es su principal desventaja, ya que solo se pueden implementar pequeños circuitos lógicos representados con un modesto número de términos producto, porque su estructura de interconexión esta fija en cuanto a que no se puede configurar la salida si se requiere que sea activo alto, activo bajo, con o sin registro. En la Figura 8 se observa el diseño de una PAL con puertas de distintos tipos.

Figura 8. Diseño de una PAL con puertas de distintos tipos.

En el mercado se manejan referencias de las PALs comerciales como la PAL16L8, PAL20L8, PAL20V8 y PAL20X8.

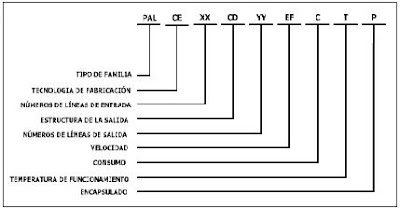

8. Nomenclatura de la PAL.

Los líderes en fabricación de PLDs, Texas Instruments y AMD, tienen una notación para identificar los dispositivos [2]. Por ejemplo, la estructura en PLD según AMD es:

Figura 9. Nomenclatura utilizada para identificar los PLD según AMD.

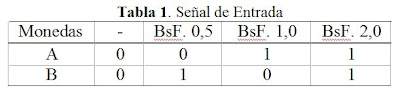

Dentro de la estructura de salida se tienen las posibilidades contenidas en la tabla 1.

Tabla 1 Tipos de Salidas de una PAL.

9. Conclusiones.

Los PAL internamente están formados por matriz de conexiones, matriz de compuertas AND programables y un arreglo de compuertas OR fijo, y se encuentran disponibles en varias tecnologías de circuitos, además de TTL bipolar de fusibles programables.

Debido a la complejidad del circuito interno de las PAL, los fabricantes implementaron un circuito simplificado para eliminar los diagramas lógicos complicados utilizando buffer de entradas, una sola línea para representar a todas las líneas de entrada de una AND, indicando los fusibles mediante una X en el punto de intersección, entre otros.

Entre los fabricantes de las PAL, se encuentran la Monolithic Memories, Inc., (MMI), National Semiconductor, Texas Instruments y AMD.

Los arreglos lógicos programables (PAL) son introducidos al mercado como un reemplazo de bajo costo para las compuertas lógicas PROM y PLA.

Las velocidad de manejo de las PAL es de 4.7 Mhz para la IBM PC hasta 50 Mhz, además existen dispositivos que operan con un retraso de propagación de la señal del orden de 5 ns.

10. Referencias Bibliográficas.

1. Torres Francisco. Circuitos Integrados de Aplicación Específica. Disponible: www2.uniovi.es/8693/documento/LECC1ce.Pdf. [Consulta: 2007, noviembre 27].

2. González, José L. Sistemas Electrónicos Digitales. Temario Volumen II. Disponible: books.google.com. [Consulta: 2007, noviembre 27].

3. Sanchis Enrique. (2002). Fundamentos y Diseño de Aplicaciones. Tecnología. Disponible: books.google.com. [Consulta: 2007, noviembre 27].

4. Montejo Miguel. Lógica Programada. Disponible: es.wikipedia.org/wiki/ Lógica _ programada - 40k. [Consulta: 2007, noviembre 27].