Basanta Ingrid

dergrid@hotmail.com

Santiago Lemus

santia90@hotmail.com

Universidad Nacional Experimental Politécnica

“Antonio José de Sucre”

Vicerrectorado Puerto Ordaz

Departamento de Ingeniería Electrónica

Maestría de Ingeniería Electrónica, Cátedra Electrónica Integrada

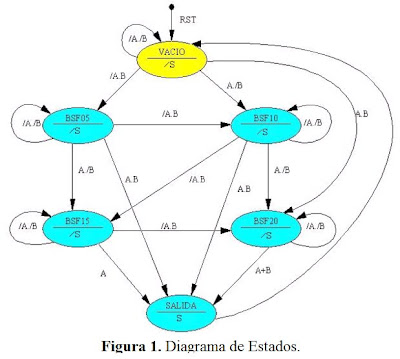

Resumen: En el presente trabajo se realiza la programación e implementación de una FPGA para el control de una máquina expendedora de refresco, la cual no acumula dinero ni da cambio. Primeramente se describe el proceso de expendio del refresco de la máquina, luego se presenta el diagrama de estado el cual se utiliza para obtener las ecuaciones booleanas y secuenciales del sistema, que a su vez permitirá construir el circuito lógico y desarrollar la codificación en VHDL para programar la FPGA Xilinx XC2S200E. Antes de realizar la implementación se presenta la simulación del código en VHDL, mediante el software ModelSim XE III 6.2g de la empresa Xilinx. Los resultados muestran que el código desarrollado se ajusta perfectamente a la lógica establecida para el funcionamiento de la máquina de refresco.

1. INTRODUCCIÓN.

Como tarea de fin de curso de la asignatura Electrónica Digital se presenta en este trabajo la programación e implementación de un FPGA en una máquina expendedora de refresco la cual posee las siguientes características: la máquina solo puede admitir dos tipos de monedas y un solo tipo billete. El costo del refresco es de 2,5 Bs.F y la máquina solo expende un tipo de refresco.

2. DESARROLLO.

Como se mencionara anteriormente la máquina expende un solo tipo de refresco siempre y cuando el usuario introduzca una cantidad de dinero igual o superior a BsF 2,5 dado que la máquina no da vuelto ni acumula la cantidad. Se pueden introducir dos tipos de monedas y un solo tipo de billete, donde las monedas son de 0,50 BsF y 1 BsF, y el billete de 2 BsF.

2.3. Diagrama de Estado.

Ahora bien, a medida que se introducen monedas a la expendedora de refresco, el estado lógico de la misma debe ir cambiando para identificar cuantas monedas ha introducido el consumidor. Estos estados se pueden definir mediante tres bits, los cuales son identificados en la Tabla 2 por Q1, Q2 y Q3.

Figura 2. Circuito Lógico Secuencial

Figura 2. Circuito Lógico Secuencial-- Project Name: Ingrid Basanta

-- Target Devices: FPGA XC2S200E

---------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity MaqRefresco is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

RST : in STD_LOGIC;

CLK : in STD_LOGIC;

S : out STD_LOGIC );

end MaqRefresco;

type ESTADOS is (VACIO, BSF05, BSF10, BSF15, BSF20, SALIDA);

attribute syn_encoding: string;

attribute syn_encoding of ESTADOS: type is "sequential";

signal ESTADOA,ESTADOSIG: ESTADOS;

begin

process (RST,CLK) --Inicia el proceso secuencial

begin

if (RST='1') then

ESTADOA <= VACIO;

Figura 3. Comportamiento para la secuencia BsF. 0,5; BsF. 1,0 y BsF. 2,0

Una vez probado el código mediante la simulación se procedió a realizar la implementación en la FPGA Xilinx XC2S200E utilizando el mismo software, donde los pines de conexión para las entradas y salidas son:

A: T11

B: L14

CLK: T9

RST: M13

S: T13

3. CONCLUSIONES.

- La utilización de los softwares de simulación facilita el diseño de los sistemas de control que utilizan dispositivos lógicos.

- Los diagramas de estados son una herramienta poderosa que permiten generar o desarrollar la programación en VHDL (o en Verilog) de los PLDs, en forma muy sencilla.

- La utilización de software de la empresa que fabrica la FPGA (en éste caso Xilinx) permite realizar la implementación con bastante sencillez, dado que éste, despues de culminado el proceso genera el código para programar la FPGA e indica los puntos de conexión de la misma.

5. BIBLIOGRAFÍAS.

[1] Tocci Ronald, (1996), "Sistemas Digitales, Principios y Aplicaciones". Prentice Hall, Sexta edición, Máxico. Pag. 833.

[2] Sánchez Inocente, (2007). “Tecnología de Computadores". Disponible: http://www.virtual.unal.edu/. [Consulta: 2007, enero, 15].

1 comentario:

muy buen proyecto

Publicar un comentario